-

Dapat mengetahui dan memahami konstruksi JFETs

-

Dapat mengetahui dan memahami karakteristik JFETs

-

Dapat membuat rangkaian sederhana dengan channel JFETs.

2. ALAT DAN BAHAN[Kembali]

| Specifications | |

| Resistance (Ohms) | 10K |

| Power (Watts) | 0.25W, 1/4W |

| Tolerance | ±5% |

| Packaging | Bulk |

| Composition | Carbon Film |

| Temperature Coefficient | 350ppm/°C |

| Lead Free Status | Lead Free |

| RoHS Status | RoHS Compliant

|

Volt meter DC merupakan alat ukur yang berfungsi untuk mengetahui beda potensial tegangan DC antara 2 titik pada suatu beban listrik atau rangkaian elektronika.

Transistor adalah komponen semikonduktor yang memiliki berbagai macam fungsi seperti sebagai penguat, pengendali, penyearah, osilator, modulator dan lain sebagainya. Transistor merupakan salah satu komponen semikonduktor yang paling banyak ditemukan dalam rangkaian-rangkaian elektronika. Boleh dikatakan bahwa hampir semua perangkat elektronik menggunakan Transistor untuk berbagai kebutuhan dalam rangkaiannya. Perangkat-perangkat elektronik yang dimaksud tersebut seperti Televisi, Komputer, Ponsel, Audio Amplifier, Audio Player, Video Player, konsol Game, Power Supply dan lain-lainnya.

Ground Berfungsi sebagai untuk meniadakan beda potensial dengan mengalirkan arus sisa dari kebocoran tegangan atau arus pada rangkaian

3. DASAR TEORI[Kembali]

Seperti yang ditunjukkan sebelumnya, JFET

adalah perangkat tiga terminal dengan satu terminal yang mampu mengendalikan

arus antara dua lainnya. Dalam pembahasan kita tentang transistor BJT

transistor npn digunakan melalui bagian utama dari analisis dan desain bagian,

dengan bagian yang dikhususkan untuk dampak menggunakan transistor pnp. Untuk

JFET transistor perangkat n-channel akan muncul sebagai perangkat menonjol,

dengan paragraf dan bagian yang dikhususkan untuk dampak penggunaan JFET

saluran-p.

Konstruksi dasar JFET n-channel ditunjukkan

pada Gambar 5.2. Perhatikan bahwa bagian utama dari struktur adalah material

tipe-n yang membentuk saluran antara lapisan tertanam dari bahan tipe-p.

Bagian atas saluran tipe-n dihubungkan melalui kontak ohmik ke terminal

disebut sebagai saluran (D), sedangkan ujung bawah bahan yang sama dihubungkan

melalui kontak ohmik ke terminal yang disebut sumber). Dua material tipe-p

dihubungkan bersama dan ke gerbang (G) terminal. Intinya, oleh karena itu,

saluran dan sumber terhubung ke ujung saluran tipe-n dan gerbang ke dua

lapisan material tipe-p. Dengan tidak adanya setiap potensi yang diterapkan

JFET memiliki dua persimpangan p-n dalam kondisi tanpa bias. Itu Hasilnya

adalah daerah penipisan di setiap persimpangan seperti yang ditunjukkan pada

Gambar 5.2 yang menyerupai wilayah yang sama dari dioda dalam kondisi tanpa

bias. Ingat juga bahwa daerah penipisan adalah wilayah itu tidak memiliki

operator gratis dan karena itu tidak dapat mendukung konduksi melalui

wilayah.

Gambar 5.2 Efek medan persimpangan transistor (JFET).

Analoginya jarang sempurna dan terkadang bisa

menyesatkan, tetapi analogi air pada Gambar 5.3 memberikan pengertian untuk

kontrol JFET di terminal gerbang dan kesesuaian terminologi yang diterapkan ke

terminal perangkat. Sumber Tekanan air dapat diibaratkan tegangan yang

diberikan dari saluran ke sumber yang diinginkan membentuk aliran air

(elektron) dari keran (sumber). "Gerbang", melalui sinyal yang diterapkan

(potensial), mengontrol aliran air (mengisi) ke "drain." Tiriskan dan terminal

sumber berada di ujung yang berlawanan dari saluran-n seperti yang ditunjukkan

pada Gambar 5.2 karena terminologi didefinisikan untuk aliran elektron.

Gambar 5.3 Analogi air untuk mekanisme kontrol JFET

VGS = 0 V, VDS Some Positive Value

Pada Gambar 5.4, tegangan positif VDS

telah diterapkan melintasi saluran dan gerbang telah terhubung langsung ke

sumber untuk membentuk kondisi VGS 0 V. The Hasilnya adalah gerbang dan

terminal sumber pada potensi yang sama dan daerah penipisan di ujung

rendah dari setiap bahan-p mirip dengan distribusi kondisi tanpa bias pada

Gambar. 5.2. Saat tegangan VDD (VDS) diterapkan, elektron akan tertarik

terminal pembuangan, menetapkan ID arus konvensional dengan arah yang

ditentukan dari Gambar 5.4. Jalur aliran muatan dengan jelas mengungkapkan

arus drain dan sumber setara (ID IS). Di bawah kondisi yang tampak pada

Gambar 5.4, aliran muatan relatif tidak dibatasi dan hanya dibatasi oleh

resistensi antara n-channel tiriskan dan sumber.

Gambar 5.4 JFET di VGS = 0 V dan VDS >0 V.

Penting untuk dicatat bahwa daerah

penipisan lebih lebar di dekat bagian atas kedua material tipe. Alasan

perubahan lebar wilayah paling baik dijelaskan melalui bantuan Gambar

5.5. Dengan asumsi resistansi seragam di saluran-n, resistansi saluran

dapat dipecah menjadi divisi-divisi yang tampak pada Gambar 5.5. Itu ID

saat ini akan menetapkan level tegangan melalui saluran seperti yang

ditunjukkan pada sosok yang sama. Hasilnya adalah bahwa daerah atas dari

bahan tipe-p akan dibalik sekitar 1,5 V, dengan daerah yang lebih rendah

hanya bias balik sebesar 0,5 V. Pembahasan tentang operasi dioda bahwa

semakin besar bias balik yang diterapkan, maka memperluas wilayah

penipisan — maka distribusi wilayah penipisan seperti yang ditunjukkan

pada Gambar 5.5. Fakta bahwa persimpangan p-n bias-balik untuk panjang

saluran menghasilkan arus gerbang nol ampere seperti yang ditunjukkan

pada gambar yang sama. Faktanya bahwa IG 0 A merupakan karakteristik

penting JFET.

Gambar 5.5 Memvariasikan bias balik

potensi melintasi persimpangan p-n

dari JFET n-channel.

Ketika tegangan VDS dinaikkan dari 0

menjadi beberapa volt, arus akan meningkat ditentukan oleh hukum Ohm dan

plot ID versus VDS akan muncul seperti yang ditunjukkan pada Gambar.

5.6. Keteraturan plot menunjukkan bahwa untuk wilayah dengan nilai yang

rendah VDS, resistansi pada dasarnya konstan. Saat VDS meningkat dan

mendekati suatu level disebut sebagai VP pada Gambar 5.6, daerah

penipisan Gambar 5.4 akan melebar, menyebabkan pengurangan yang nyata

pada lebar saluran. Jalur konduksi yang berkurang menyebabkan resistensi

terhadap kenaikan dan kurva pada grafik Gambar 5.6 terjadi. Semakin

horizontal kurva, semakin tinggi resistansi, menunjukkan bahwa

resistansi mendekati ohm "tak terbatas" di wilayah horizontal. Jika VDS

dinaikkan ke level di mana

tampak bahwa dua daerah penipisan akan "menyentuh" seperti yang

ditunjukkan pada Gambar 5.7, kondisi yang disebut pinch-off akan

terjadi. Tingkat VDS yang menetapkan kondisi ini disebut sebagai

tegangan pinch-off dan dilambangkan dengan VP seperti yang ditunjukkan

pada Gambar.

5.6. Pada kenyataannya, istilah pinch-off adalah istilah yang keliru

karena menunjukkan ID saat ini

terjepit dan turun ke 0 A. Seperti yang ditunjukkan pada Gambar 5.6,

bagaimanapun, ini hampir tidak

case - ID mempertahankan tingkat saturasi yang didefinisikan sebagai

IDSS pada Gambar 5.6. Pada kenyataannya sangat saluran kecil masih ada,

dengan arus dengan kepadatan yang sangat tinggi. Fakta bahwa ID

melakukannya tidak jatuh saat pinch-off dan mempertahankan tingkat

saturasi yang ditunjukkan pada Gambar 5.6 diverifikasi oleh fakta

berikut: Tidak adanya arus drain akan menghilangkan kemungkinan level

potensial yang berbeda melalui material saluran-n untuk menetapkan

berbagai tingkat bias balik di sepanjang persimpangan p-n. Hasilnya

adalah kerugian distribusi wilayah penipisan yang menyebabkan pinch-off

di tempat pertama.

Gambar 5.6 Gambar 5.7

ID versus VDS untuk VGS 0 V Pinch-off (VGS = 0 V, VDS = VP)

Saat VDS ditingkatkan melampaui VP,

wilayah pertemuan dekat antara keduanya daerah penipisan akan bertambah

panjangnya di sepanjang saluran, tetapi tingkat ID tetap pada dasarnya

sama. Intinya, oleh karena itu, begitu VDS VP JFET memiliki karakteristik

sumber arus. Seperti yang ditunjukkan pada Gambar 5.8, arus diperbaiki di

ID IDSS, tetapi tegangan VDS (untuk level VP) ditentukan oleh beban yang

diterapkan.

Pilihan notasi IDSS berasal dari fakta

bahwa itu adalah Drain-to-Source arus dengan koneksi hubung singkat dari

gerbang ke sumber. Saat kami terus menyelidiki karakteristik perangkat,

kami akan menemukan bahwa:

IDSS is the maximum drain current for a JFET and is defined by the

conditions

VGS = 0 V

and VDS > |VP|.

Perhatikan pada Gambar 5.6 bahwa VGS 0

V untuk seluruh panjang kurva. Beberapa berikutnya paragraf akan

menjelaskan bagaimana karakteristik Gambar 5.6 dipengaruhi oleh

perubahan di level VGS.

VGS < 0 V

Gambar 5.8 Sumber saat ini

setara untuk VGS 0 V,

VDS VP.

Tegangan dari gerbang ke sumber,

dilambangkan dengan VGS, adalah tegangan pengontrol JFET.

Sama seperti berbagai kurva untuk IC versus VCE yang ditetapkan untuk

berbagai tingkat IB transistor BJT, kurva ID versus VDS untuk berbagai

level VGS dapat dikembangkan untuk JFET. Untuk perangkat n-channel

pengontrol tegangan VGS dibuat lebih dan lebih negatif dari level VGS 0

V. Dengan kata lain, terminal gerbang akan diatur di tingkat potensial

yang lebih rendah dan lebih rendah dibandingkan dengan sumbernya.

Gambar 5.9 Penerapan

tegangan negatif ke gerbang a

JFET.

Gambar 5.10 Karakteristik n-Channel JFET

dengan IDSS = 8 mA dan VP = 4 V

Dalam Gambar 5.9, tegangan negatif 1 V

telah diterapkan antara gerbang dan terminal sumber untuk VDS level

rendah. Pengaruh VGS bias negatif yang diterapkan adalah untuk

menetapkan daerah penipisan yang serupa dengan yang diperoleh dengan

VGS 0 V tetapi lebih rendah tingkat VDS. Oleh karena itu, hasil dari

penerapan bias negatif pada gerbang akan tercapai tingkat saturasi di

tingkat yang lebih rendah dari VDS seperti yang ditunjukkan pada

Gambar 5.10 untuk VGS 1 V. Tingkat kejenuhan yang dihasilkan untuk ID

telah berkurang dan pada kenyataannya akan terus menurun karena VGS

dibuat semakin negatif. Perhatikan juga pada Gambar 5.10 bagaimana

tegangan pinchoff terus turun secara parabola karena VGS menjadi

semakin banyak. negatif. Akhirnya, VGS saat VGS VP akan cukup negatif

untuk dibangun tingkat saturasi yang pada dasarnya 0 mA, dan untuk

semua keperluan praktis perangkat telah "dimatikan". Singkatnya :

Tingkat VGS yang menghasilkan ID = 0 mA ditentukan oleh VGS = VP,

dengan VP

menjadi tegangan negatif untuk perangkat saluran-n

dan tegangan positif untuk

JFET saluran-p.

Pada sebagian besar lembar

spesifikasi, tegangan pinch-off ditetapkan sebagai VGS (mati)

daripada VP. Lembar spesifikasi akan ditinjau nanti di bab saat

primer elemen perhatian telah diperkenalkan. Wilayah di sebelah

kanan pinch-off lokus Gambar 5.10 adalah wilayah yang biasanya

digunakan dalam penguat linier (penguat dengan distorsi minimum dari

sinyal yang diterapkan) dan biasanya disebut sebagai arus konstan,

saturasi, atau wilayah amplifikasi linier.

Voltage-Controlled Resistor

Daerah di sebelah kiri lokus pinch-off

pada Gambar 5.10 disebut sebagai ohmik atau wilayah resistansi

yang dikontrol tegangan. Di wilayah ini JFET sebenarnya dapat digunakan

sebagai resistor variabel (mungkin untuk sistem kontrol penguatan

otomatis) yang resistansi dikendalikan oleh tegangan gerbang-ke-sumber

yang diterapkan. Perhatikan pada Gambar 5.10 bahwa kemiringan setiap

kurva dan oleh karena itu resistansi perangkat antara saluran dan sumber

untuk VDS VP adalah fungsi dari tegangan VGS. Saat VGS menjadi lebih dan

lebih negatif, kemiringan setiap kurva menjadi semakin horizontal,

sesuai dengan peningkatan level resistensi. Persamaan berikut akan

memberikan perkiraan pertama yang baik ke level resistansi dalam hal

tegangan yang diberikan VGS.

Pers (5.1)

Dimana ro adalah resistensi dengan VGS

0 V dan rd resistensi pada tingkat tertentu dari VGS. Untuk JFET

n-channel dengan ro sama dengan 10 k (VGS 0 V, VP 6 V), Persamaan.

(5.1) akan menghasilkan 40 k pada VGS 3 V.

Perangkat p-Channel

JFET saluran-p dibangun dengan cara

yang persis sama seperti perangkat saluran-n pada Gambar 5.2, tetapi

dengan pembalikan bahan jenis-p dan n seperti yang ditunjukkan pada

Gambar 5.11.

Gambar 5.11 p-Channel JFET

Arah arus yang ditentukan dibalik,

seperti polaritas aktual untuk tegangan VGS dan VDS. Untuk perangkat

saluran-p, saluran akan dibatasi dengan meningkatkan tegangan positif

dari gerbang ke sumber dan notasi subskrip ganda untuk VDS akan

menghasilkan tegangan negatif untuk VDS pada karakteristik Gambar

5.12, yang memiliki IDSS sebesar 6 mA dan tegangan pinch-off VGS 6 V.

Jangan biarkan minus Tanda-tanda VDS membingungkan Anda. Mereka hanya

menunjukkan bahwa sumbernya memiliki potensi yang lebih tinggi

daripada saluran pembuangan.

Gambar 5.12 Karakteristik p-Channel JFET dengan IDSS = 6 mA dan

VP = 6 V

Perhatikan pada tingkat VDS yang

tinggi bahwa kurva tiba-tiba naik ke tingkat yang tampaknya tidak

dibatasi. Kenaikan vertikal merupakan indikasi bahwa telah terjadi

breakdown dan arus melalui saluran (dalam arah yang sama seperti

biasanya) sekarang dibatasi hanya oleh sirkuit eksternal. Meskipun

tidak muncul pada Gambar 5.10 untuk perangkat saluran-n, hal itu

terjadi untuk perangkat saluran-n jika tegangan yang cukup

diterapkan. Wilayah ini dapat dihindari jika level VDSmax dicatat

pada spesifikasi lembar dan desainnya sedemikian rupa sehingga

tingkat VDS yang sebenarnya kurang dari nilai ini untuk semua nilai

VGS.

Symbols

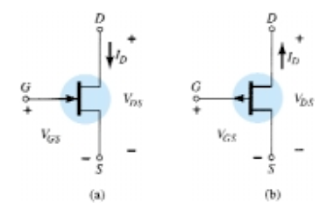

Simbol grafik untuk JFET saluran-n

dan saluran-p disediakan pada Gambar 5.13. Perhatikan bahwa panah

menunjuk ke dalam perangkat saluran-n dari Gambar 5.13a untuk

mewakili arah aliran IG jika p-n junction bias maju. Untuk perangkat

p-channel (Gbr. 5.13b) satu-satunya perbedaan dalam simbol adalah

arah panah.

Gambar 5.13 JFET symbols: (a)

n-channel; (b) p-channel

Ringkasan

Sejumlah parameter dan hubungan

penting diperkenalkan di bagian ini. Beberapa yang akan sering muncul

dalam analisis untuk mengikuti bab ini dan selanjutnya untuk JFET

n-channel meliputi yang berikut ini:

Arus maksimum didefinisikan

sebagai IDSS dan terjadi ketika VGS 0 V dan VDS | VP | seperti

yang ditunjukkan pada Gambar 5.14a. Untuk tegangan

gerbang-ke-sumber, VGS kurang dari (lebih negatif dari) pinch-off

tingkat, arus drain adalah 0 A (ID 0 A) seperti yang terlihat pada

Gambar. 5.14b. Untuk semua level VGS antara 0 V dan level

pinch-off, ID saat ini akan kisaran antara IDSS dan 0 A,

masing-masing, seperti yang ditinjau oleh Gambar. 5.14c. Untuk

JFET p-channel, daftar serupa dapat dikembangkan

Gambar 5.14 (a) VGS = 0 V, ID = IDSS;

(b) batas waktu (ID = 0 A) VGS kurang dari level pinch-off;

(c) ID ada antara 0 A dan IDSS

untuk VGS kurang dari atau sama dengan 0 V.

dan lebih besar dari pinch-off

tingkat.

A. Prosedur Percobaan

Step 1:SUSUN dan SIAPKAN KOMPONEN

Step 2: RANGKAI KOMPONEN

Step 3: MULAI SIMULASI PADA PROTEUS

Step 4: AMATI RANGKAIAN YANG DIBUAT

B. Rangkaian Simulasi

EXAMPLE 5.1

Buat sketsa kurva transfer yang ditentukan oleh IDSS 12 mA dan VP 6 V !

SOLUSI :

Dua titik plot ditentukan oleh

IDSS = 12 mA dan VGS = 0 V

dan ID = 0 mA dan VGS = VP

Pada VGS = VP / 2 = 6 V / 2 = 3 V arus drain akan ditentukan oleh ID = IDSS

/ 4 = 12 mA / 4 = 3 mA. Di ID = IDSS / 2 = 12 mA / 2 = 6 mA

gerbang-ke-sumber tegangan ditentukan oleh VGS 0,3VP 0,3 (6 V) 1,8 V.

Keempat titik plot didefinisikan dengan baik pada Gambar 5.16 dengan kurva

transfer lengkap.

Gambar 5.16 Kurva transfer untuk Contoh 5.1.

EXAMPLE 5.2

Buat sketsa kurva transfer untuk perangkat saluran-p dengan IDSS 4 mA dan VP 3

V.

SOLUSI :

Pada VGS VP / 2 3 V / 2 1,5 V, ID IDSS / 4 4 mA / 4 1 mA. Di ID IDSS / 24 mA

/ 2 2 mA, VGS 0,3VP 0,3 (3 V) 0,9 V. Kedua titik plot muncul pada Gambar.

5.17 bersama dengan poin-poin yang ditentukan oleh IDSS dan VP.

Gambar 5.17 Kurva transfer untuk Contoh 5.2

D. LINK DOWNLOAD

Problem No. 1

1. Gambarkan konstruksi dasar JFET saluran-p

Jawab :

Problem No. 8

8. Secara umum, beri komentar tentang polaritas berbagai tegangan dan arah

arus untuk JFET n-channel versus JFET p-channel

Jawab :

Saluran atau Kanal pada jenis ini terbentuk dari bahan semikonduktor tipe N dengan satu ujungnya adalah Source (S) dan satunya lagi adalah Drain (D). Mayoritas pembawa muatan atau Carriers pada JFET jenis Kanal-N ini adalah Elektron.

Saluran pada JFET jenis Kanal-P terbuat dari Semikonduktor tipe P. Mayoritas pembawa muatannya adalah Hole. Bagian Gate atau Gerbang (G) dan Subtrate-nya terbuat dari bahan Semikonduktor tipe N.

Pilihan Ganda[Kembali]

1. Gambar dibawah ini adalah JFETs channel .........

A. m

B. n

C. o

D. p

E. q

2. Gambar di bawah ini merupakan JFETS channel .....

Komentar

Posting Komentar